| All returns accepted | ReturnsNotAccepted |

|---|---|

| Brand | HP/Agilent/Keysigh |

| Unit Type | Unit |

| MPN | 16510B |

| Country/Region of Manufacture | United States |

| Unit Quantity | 1 |

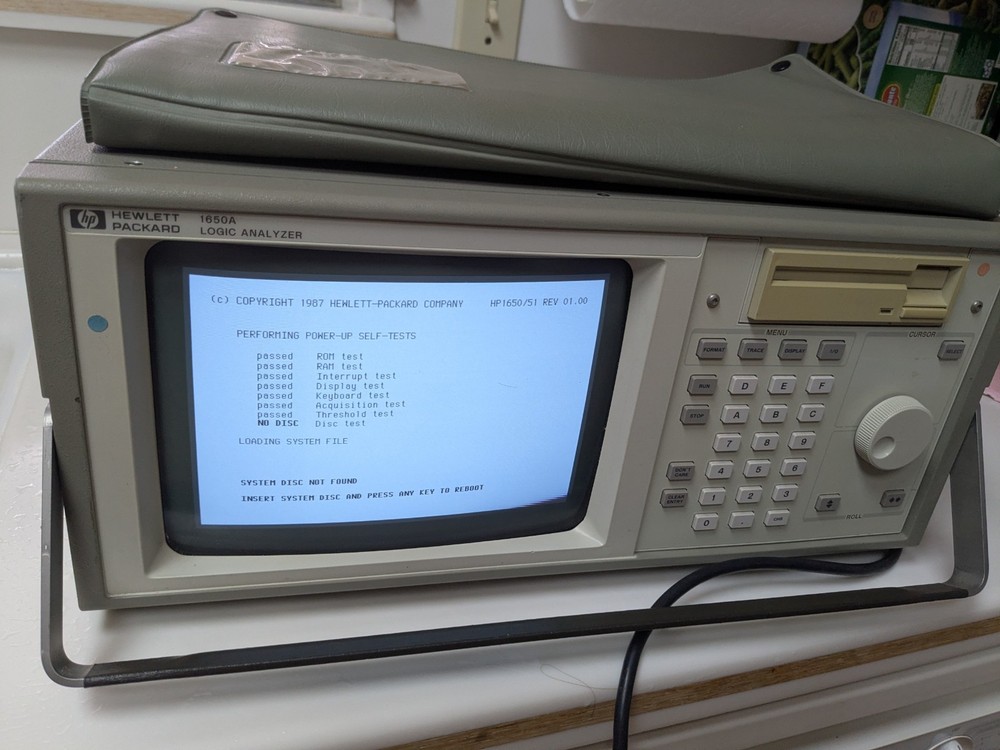

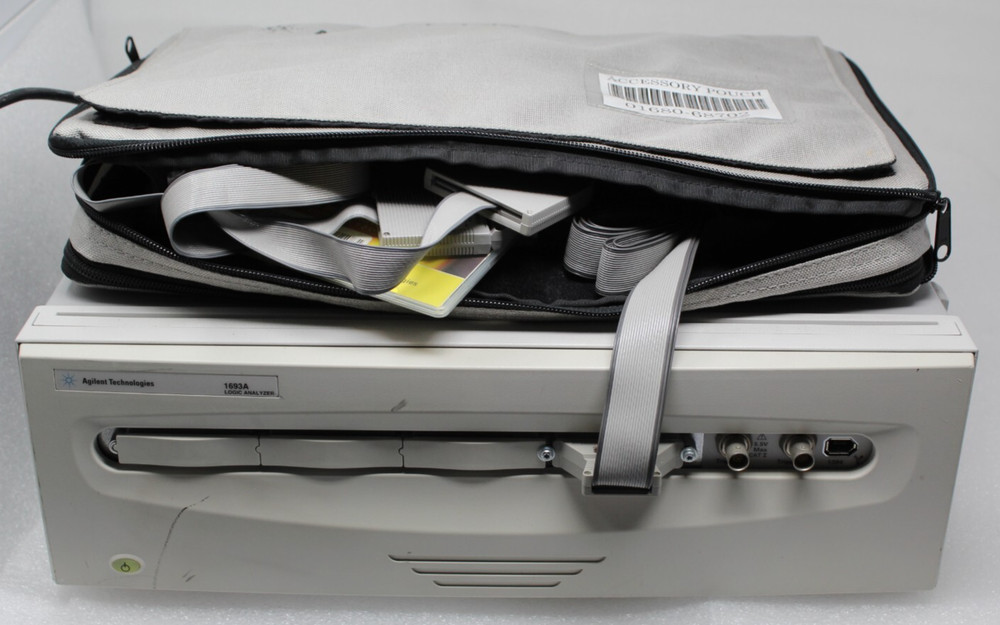

Check the listing for details. HP/Agilent/Keysight 16510B Logic Analyzer 80 Ch Card. Condition: Used. Listed at 82.50 USD. he HP 16510B State/Timing Module is an 80 channel, 35 MHz state, 100 MHz timing logic analyzer. It can be configured as two independent state analyzers, or as one state and one timing analyzer.Simultaneous state/state, or simultaneous state/timing analysisTime interval; number of states; pattern search; minimum, maximum, and average time interval statisticsUses transitional timing to store data only when there is a transitionFive clock inputs, 4 clock qualifiers, storage qualification, time and number of state tagging, and prestoreSmall lightweight probingProbes minimum swing: 600 mVp-pState modeClock Repetition Rate: Single phase is 35 MHz maximum. With time or state counting, minimum time between states is 60 nsClock Pulse Width: ≥10 ns at thresholdSetup Time: Data must be present prior to clock transition, ≥10 nsHold Time: Data must be present after rising clock transition on all pods; 0 ns. Data must be present after falling clock transition on pods 1,3 and 5; 0 ns. Data must be present after falling clock transition on pods 2 and 4; 1 nsTiming mode minimum detectable glitch: 5 ns wide at the thresholdProbes characteristicsInput RC: 100 KW ±2% shunted by approximately 8 pF at the probe tipTTL Threshold Preset: +1.6 voltsECL Threshold Preset: -1.3 voltsThreshold Range: -9.9 to +9.9 volts in 0.1V incrementsThreshold Setting: Threshold levels may be defined for pods 1, 2, and 3 on an individual basis and one threshold may be defined for pods 4 and 5Minimum Input Overdrive: 250 mV or 30% of the input amplitude, whichever is greaterMaximum Voltage: ±40 volts peakDynamic Range: ±10 volts about the thresholdState analysisData acquisition: 1024 samples / channelClocks: Five clocks are available and can be used by either one or two state analyzers at any timeClock Qualifier: The high or low level of up to four clocks can be ANDed with the clock specification. Setup time: 20 ns; hold time: 5 nsPattern Recognizers: Each recognizer is the AND combination of bit (0, 1, or X) patterns in each label. Eight pattern recognizers are available when one state analyzer is on. Four are available to each analyzer when two state analyzers are onRange Recognizers: Recognizes data which is numerically between or on two specified patterns (ANDed combination of 0s and/or 1s)Qualifier: A user-specified term that can be anystate, nostate, a single pattern recognizer, range recognizer, or logical combination of pattern and range recognizersSequence Levels: There are eight levels available to determine the sequence of events required for trigger. The trigger term can occur anywhere in the first seven sequence levelsBranching: Each sequence level has a branching qualifier. When satisfied, the analyzer will restart the sequence or branch to another sequence levelOccurrence Counter: Sequence qualifier may be specified to occur up to 65535 times before advancing to the next levelStorage Qualification: Each sequence level has a storage qualifier that specifies the states that are to be storedEnable/Disable: Defines a window of post-trigger storagePrestore: Stores two qualified states that precede states that are storedTaggingState tagging: Counts the number of qualified states between each stored state. Maximum count is 4.4 x 1012Time tagging: Measures the time between stored states, relative to either the previous state or the trigger. Maximum time between states is 48 hoursTiming analysisTransitional timing mode—Sample is stored in acquisition memory only when the data changes. Sample period: 10 ns, maximum time covered by data: 5000 seconds, minimum time covered by data: 10.24 µsGlitch capture mode—Data sample and glitch information stored every sample period. Sample period: 20 ns to 50 ms, memory depth: 512 samples / channel, time covered by data: sample period x 512Waveform display—Sec/div: 10 ns to 100 s; 0.01% resolution, delay: ‑2500 s to 2500 s, maximum number of displayed waveforms: 24Trigger—Asynchronous pattern: Trigger on an asynchronous pattern less than or greater than specified duration, Greater than duration: minimum duration is 30 ns to 10 ms, Less than duration: maximum duration is 40 ns to 10 ms, Glitch/edge triggering: trigger on glitch or edge following valid duration of asynchronous pattern while the pattern is still presentUser interface control devices: knob on front panel, touchscreen fields, optional mouseHP-IB and RS-232C interfaces for hardcopy printouts and control by a host computer